# Proceedings of the First International Workshop on Sustainable Ultrascale Computing Systems (NESUS 2014) Porto, Portugal

Jesus Carretero, Javier Garcia Blas Jorge Barbosa, Ricardo Morla (Editors)

August 27-28, 2014

# **Volume Editors**

Jesus Carretero University Carlos III Computer Architecture and Technology Area Computer Science Department Avda Universidad 30, 28911, Leganes, Spain E-mail: jesus.carretero@uc3m.es

Javier Garcia Blas University Carlos III Computer Architecture and Technology Area Computer Science Department Avda Universidad 30, 28911, Leganes, Spain E-mail: fjblas@arcos.inf.uc3m.es

Jorge Barbosa Faculdade de Engenharia da Universidade do Porto (FEUP) Departamento de Engenharia Informatica Rua Dr. Roberto Frias, s/n 4200-465 Porto, Portugal E-mail: jbarbosa@fe.up.pt

Ricardo Morla Faculdade de Engenharia da Universidade do Porto (FEUP) ECE department Rua Dr. Roberto Frias, s/n 4200-465 Porto, Portugal E-mail: rmorla@fe.up.pt

Published by: Computer Architecture,Communications, and Systems Group (ARCOS) University Carlos III Madrid, Spain http://www.nesus.eu

# ISBN: 978-84-617-2251-8

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

This document also is supported by:

$\langle \bigcirc \rangle$

Printed in Madrid - November 2014

# Preface

#### Network for Sustainable Ultrascale Computing (NESUS)

We are very excited to present the proceedings of the First International Workshop on Sustainable Ultrascale Computing Systems (NESUS 2014), a workshop created to reflect the research and cooperation activities made in the NESUS COST Action (IC1035) (www.nesus.eu), but open to all the research community working in large/ultra-scale computing systems. It was held in Porto (Portugal) on August 27-28, 2014.

The goal in scalable and sustainable technology today is to have on the one hand large parallel supercomputers, named Exascale computers, and on the other hand, to have very large data centers with hundreds of thousands of computers coordinating with distributed memory systems. Ultimately, NESUS idea is to have both architectures converge to solve problems in what we call ultrascale. Ultrascale systems combine the advantages of distributed and parallel computing systems. The former is a type of computing in which many tasks are executed at the same time coordinately to solve one problem, based on the principle that a big problem can be divided into many smaller ones that are simultaneously solved. The latter system, in both grid and cloud computing, uses a large number of computers organized into clusters in a distributed infrastructure, and can execute millions of tasks at the same time usually working on independent problems and big data. The applications of these systems and the benefits they can yield for society are enormous, according to the researchers, who note that this type of computing will help conduct studies about genomics, new materials, simulations of fluid dynamics used for atmospheric analysis and weather forecasts, and even the human brain and its behavior.

The goal of the NESUS Action is to establish an open European research network targeting sustainable solutions for ultrascale computing aiming at cross fertilization among HPC, large scale distributed systems, and big data management. Ultrascale systems are envisioned in NESUS as large-scale complex systems joining parallel and distributed computing systems that will be two to three orders of magnitude larger that today's systems. The EU is already funding large scale computing systems research, but it is not coordinated across researchers, leading to duplications and inefficiencies. The network will contribute to glue disparate researchers working across different areas and provide a meeting ground for researchers in these separate areas to exchange ideas, to identify synergies, and to pursue common activities in research topics such as sustainable software solutions (applications and system software stack), data management, energy efficiency, and resilience. Some of the most active research groups of the world in this area are members of this NESUS Action. This Action will increase the value of these groups at the European-level by reducing duplication of efforts and providing a more holistic view to all researchers, it will promote the leadership of Europe, and it will increase their impact on science, economy, and society.

The scientific objective of NESUS is to study the challenges presented by the next generation of ultrascale computing systems to enhance their sustainability. These systems, which will be characterized by their large size and great complexity, present significant challenges, from their construction to their exploitation and use. We try to analyze all the challenges there are and see how they can be studied holistically and integrated, to be able to provide a more sustainable system. The challenges that this type of computing poses affect aspects such as scalability, the programming models used, resilience to failures, energy management, the handling of large volume of data, etc. One of the NESUS goals is to find the way that all solutions that are proposed can be transmitted to user applications with the minimum possible redesign and reprogramming effort.

The project began last March with 29 European countries, but at present consists of 39 European countries and six countries from other continents. It now involves nearly 200 scientists, almost 40% of whom are young researchers, because

one essential goal of these Actions is to promote and create an ecosystem of scientists who can work on these matters in the European Union in the future.

The project have already held two important meetings: one for work groups in Madrid in July and another in Oporto (Portugal) at the end of August, attended by representatives of the research groups that participate as well as Project Officers from the EU's H2020 program. By reducing duplication of work and providing a more comprehensive vision of all the researchers, this COST Action hopes to increase the value of these groups at the European level, promoting European leadership in this area of knowledge, as well as enhancing its impact on science, the economy and society.

This Action, which concludes in 2018, aims to produce a catalogue of open source applications that are being developed by the members of the Action and which will serve to demonstrate new ultrascale systems and take on their main challenges. In this way, anyone will be able to use these applications to test them in their systems and demonstrate their level of sustainability.

Prof. Jesus Carretero University Carlos III of Madrid NESUS Chair

November 2014

# **COST Action IC1305**

2014 | 2018

# Network for Sustainable Ultrascale Computing

# Aim

Coordinate European efforts for proposing realistic solutions addressing major challenges of building sustainable Ultrascale Computing Systems (UCS) with a holistic approach.

To:

- 1. Increase EU research in the field of sustainable ultrascale computing.

- 2. Give coherence to the European ICT research agenda related to sustainability.

- 3. Build a multi-disciplinary forum for cross-fertilization of ideas for sustainable ultrascale computing.

# Scientific Workplan

# Topics

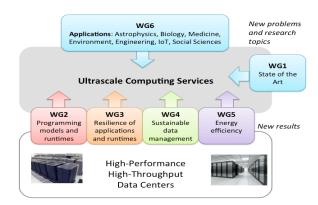

- WG1: New techniques to enhance sustainability holistically.

- WG2: Promoting new sustainable programming and execution models in the context of rapidly changing underlying computing architecture.

- WG3: Innovative techniques to deal with hardware and system software failures or intentional changes within the complex system environment.

- WG4: Study data management lifecycle on scalable architectures in a synergistic approach to pave the way towards sustainable UCS.

- WG5: Explore the design of metrics, analysis, frameworks and tools for putting energy awareness and energy efficiency at the next stage.

- WG6: Identify algorithms, applications, and services amenable to ultrascale systems and to study the impact of application requirements on the sustainable ultrascale system design.

# Activities

- Research activities though WGs

- Set up collaborations through STSM and internships

- Training schools and PhD forum

- Meetings for WGs and MC

- Dissemination and cooperation with industry and stakeholders.

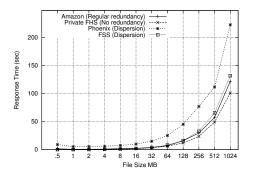

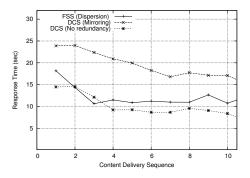

- Publications, conference organization, industry seminars, …

Information and Communication Technologies (ICT)

Participating countries: 45 EU COST countries: 33

AT, BA, BE, BG, BO, CH, CY, DE, DK, EE, EL, ES, FI, FR, HR, HU, IE, IL, IT, LT, LU, MK, MT, NL, NO, PL, PT, RO, SI, SK, SE, TR, UK

# **NNC countries: 6**

AL, AM, MD, MO, RU, UA

**Global Collaboration: 6**

AU, CA, CO, IN, MX, US

# **Contact details**

Chair of the Action Jesus Carretero jesus.carretero@uc3m.es

Website www.nesus.eu

# WORKSHOP PROGRAM

# First NESUS Workshop (NESUS 2014)

- Juan-Antonio Rico-Gallego, Juan-Carlos Diaz-Martin

Improving the Performance of the MPI Allreduce Collective Operation through Rank Renaming

- 7 Fabrizio Marozzo, Domenico Talia, Paolo TrunfioA Workflow-oriented Language for Scalable Data Analytics

- 13 Georgios L. Stavrinides, Helen KaratzaScheduling Real-Time Jobs in Distributed Systems Simulation and Performance Analysis

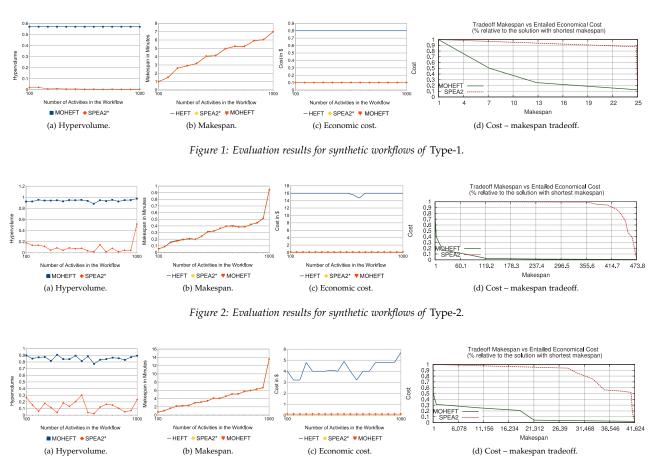

- 19 Juan J. Durillo, Radu ProdanBi-objective Workflow Scheduling in Production Clouds: Early Simulation Results and Outlook

- 27 *Zorislav Shoyat* An Approach Towards High Productivity Computing

- 33 Svetislav Momcilovic, Aleksandar Ilic, Nuno Roma, Leonel Sousa

Efficient Parallel Video Encoding on Heterogeneous Systems

- Raimondas Ciegis, Vadimas Starikovicius, Andrej Bugajev

On Efficiency of the OpenFOAM-based Parallel Solver for the Heat Transfer in Electrical Power Cables

- 43 Juan-Carlos Diaz-Martin, Juan A. Rico-Gallego

On the Performance Of the Thread-Multiple Support Level In Thread-Based MPI

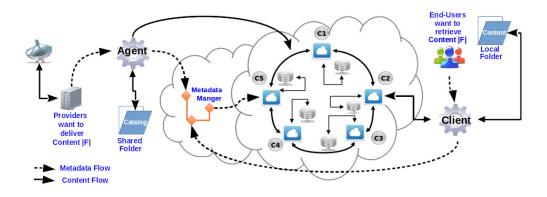

- 49 Jose Luis Gonzalez, Victor J. Sosa-Sosa, Jesus Carretero, Luis Miguel Sanchez

Content Delivery and Sharing in Federated Cloud Storage

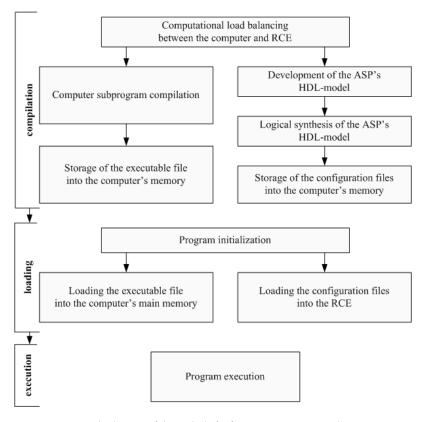

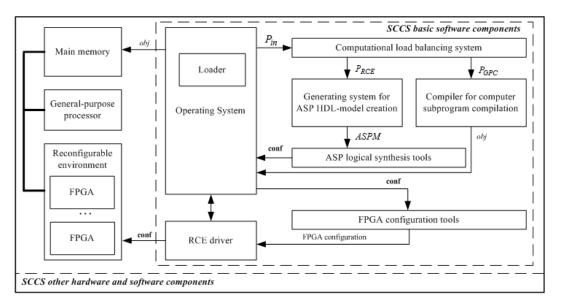

- 55 Anatoliy Melnyk, Viktor Melnyk Improvement of Heterogeneous Systems Efficiency Using Self-Configurable FPGA-based Computing

- 61 Biljana Stamatovic, Roman TrobecData parallel algorithm in finding 2-D site percolation backbones

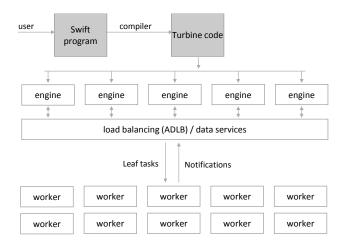

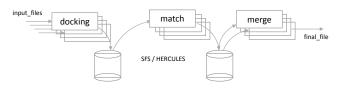

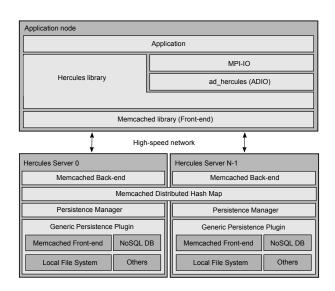

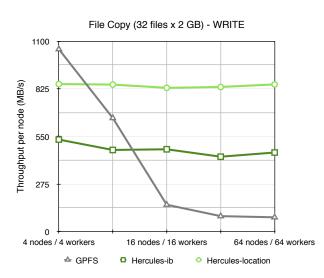

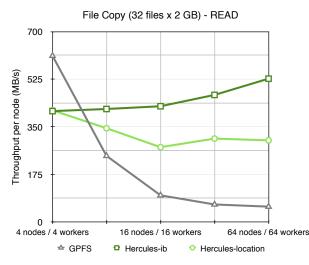

- 67 Francisco Rodrigo Duro, Javier Garcia Blas, Florin Isaila, Justin Wozniak, Jesus Carretero, Rob Ross Exploiting data locality in Swift/T workflows using Hercules

# 73 List of Authors

# Improving the Performance of the MPI\_Allreduce Collective Operation through Rank Renaming

JUAN-ANTONIO RICO-GALLEGO

JUAN-CARLOS DÍAZ-MARTÍN

University of Extremadura, Spain jarico@unex.es University of Extremadura, Spain juancarl@unex.es

Abstract

Collective operations, a key issue in the global efficiency of HPC applications, are optimized in current MPI libraries by choosing at runtime between a set of algorithms, based on platform-dependent beforehand established parameters, as the message size or the number of processes. However, with progressively more cores per node, the cost of a collective algorithm must be mainly imputed to process-to-processor mapping, because its decisive influence over the network traffic. Hierarchical design of collective algorithms pursuits to minimize the data movement through the slowest communication channels of the multi-core cluster. Nevertheless, the hierarchical implementation of some collectives becomes inefficient, and even impracticable, due to the operation definition itself. This paper proposes a new approach that departs from a frequently found regular mapping, either sequential or round-robin. While keeping the mapping, the rank assignation to the processes is temporarily changed prior to the execution of the collective algorithm. The new assignation makes the communication pattern to adapt to the communication channels hierarchy. We explore this technique for the Ring algorithm when used in the well-known MPI\_Allreduce collective, and discuss the obtained performance results. Extensions to other algorithms and collective operations are proposed.

Keywords MPI Collectives, Parallel Algorithms, Message Passing Interface, Multi-core Clusters

#### I. INTRODUCTION

MPI [1] collective functions involve a group of processes communicating by message passing in an isolated context, known as *communicator*. Each process of a communicator is identified by its *rank*, an integer number ranging from 0 to P - 1, where P is the size of the communicator. The optimisation of collectives is a key issue in HPC applications. A collective operation can be executed by different algorithms, each suitable for a given network technology, communicator size, message size, etc. For example, in the MPICH library [2], the implementation of *MPI\_Allreduce* uses two algorithms for medium and large messages when the number of processes is a power of two, namely *Recursive Doubling* and *Ring*. The switch from the first to the second algorithm is done at execution time, with platform-dependent beforehand established message size and process number thresholds.

Current parallel systems are composed of multi-core nodes connected by a high performance network. The communication cost between two MPI ranks depends on their location, being lower if they share memory, and higher if they are in different nodes. Therefore the performance of an application depends on the assignation of the ranks to the processors of the cluster (mapping). In general, two types of mapping cover the necessities of most applications: *sequential* and *round-robin*. In the sequential mapping, ranks bind to processors so that a domain is completed (e.g. socket or node) before moving to the next domain. In round-robin, ranks are bound to domains by rotating on the existing domains.

Mapping affects to the performance of the underlying algorithms of collective operations. Interestingly, a given mapping may favour an algorithm and, at the same time, being harmful to another algorithm, not matter if both are used in the implementation of the same collective. For example, in the implementation of the *allreduce* operation in MPICH, referred above, the Recursive Doubling algorithm shows a better performance when the mapping is round-robin, while the Ring algorithm runs faster under the sequential mapping.

An approach to the issue of collectives performance is building algorithms that are aware of the different capacities of the available communication channels, as shared memory and network. These algorithms, known as *hierarchical*, stand on minimizing the communications through the slower channels, but the implementation for some collectives as *allgather* is not as effective as expected, even impracticable, and hence it is not provided in well-known MPI libraries as Open MPI [3].

This paper describes a new approach to the optimization of collectives in multi-core clusters. The goal is to obtain the best possible communication throughput. For instance, in the Ring algorithm, the communication takes place between consecutive ranks. If consecutive ranks are mapped to different nodes, all the communications progress through the network. Instead, a schedule of consecutive ranks to processes placed in the same multi-core node favours the much more efficient shared memory communication. Our method is based on a temporal reassignment of ranks. That neither modifies the algorithm nor the physical mapping. Instead, it is carried out by means of a transformation function prior to the execution of the algorithm. The function is simple and efficient, and converts a sequential mapping to round-robin and vice versa only during the execution of the algorithm.

This paper focuses on the *Ring* algorithm in the context of the *allreduce* operation. Besides, the methodology described is directly applicable to other algorithms used in the implementation of MPI

collectives. Platform considered is characterized by *P*, the number of processors (or processes involved in the operation), and *M*, the number of nodes in the cluster. Q = P/M is the number of processors per node. Two channels are considered in the system, shared memory and network, with different performance. The study is conducted under two different mappings, sequential and round-robin, under the assumption of a homogeneously distributed number of processes over the nodes of the system. A hierarchical implementation of the algorithm is examined as well. The attained cost reduction depends on the number of nodes and the number of processes per node. In the used experimental platform, even with a small number of processes and nodes, the improvement reaches up to  $2 \times$  for long messages.

With respect to the structure of this article, following this introduction, section II reviews proposals of optimization of collective operations in a broad range of platforms. Section III studies the allreduce *Ring* algorithm in multi-core clusters based on the incoming mapping, and also a hierarchical allreduce implementation. The section exposes our proposal to improve the performance of the algorithm and the section IV outlines extensions to cases not covered in this paper. Section V shows the obtained performance figures, and section VI concludes the paper.

#### II. Related Work

MPI collectives performance is a key issue in high performance computing applications, and significant work has been invested in their design and optimization. Collectives in the MPI standard can be implemented from several of a set of algorithms available.

For instance, MPI\_Allreduce can be implemented using the Recursive Doubling algorithm, that improves the latency when P is a power of two for small messages because is optimum with regard to the number of stages, however, the Ring algorithm performs better for larger messages. Both algorithms are also used in the implementation of MPI\_Allgather, for which, in addition, other proposed algorithms improve the performance when requirements related to message size, process number or hardware and network technologies are met. Bruck algorithm [4] is more efficient for very short messages, even though it needs additional temporal memory, Neighbour Exchange algorithm in [5] requires half the stages than the Ring algorithm when the number of processes is even, and it exploits the piggy-backing feature of the TCP/IP protocols, as well as the Dissemination algorithm, proposed in [6], based on processes pairwise exchange of messages. Also related to the improvement of the performance by exploiting some networks capabilities, Mamidala et al. [7] evaluate the RDMA capacity for allowing concurrent direct memory access by the processes either in the same or different node of a multi-core cluster. Ma et al. [8] discuss the intra-node processes direct copy communication through shared memory by using the capacities of the operating system, and in [9] evaluate its impact in the collectives operations. Kielmann et al. [10] focus on the optimization of collective communications for clustered wide area systems.

The use of several algorithms in the same collective, based on system dependant beforehand established thresholds for message size and number of processes is shown by Thakur et al. in work [11] in a monoprocessor cluster of workstations. This approach has been adopted by the MPICH library, and it is available in the Open MPI library through its Modular Component Architecture [12]. Vadhiyar et al. [13] evaluate such improvement of performance through previous executed series of experiments conducted in an specific platform.

Multi-core clusters introduce a new actor in the scene. Performance becomes dependant on the effective use of the different communication channels. Hierarchical algorithms are specifically built to minimize the use of slower communication channels, and usually execute in several stages [14]. The process group splits in subgroups, with a local root per subgroup. Processes in a subgroup communicate through the faster communication channel, usually shared memory, hence, a subgroup is assigned to a node in the system. The application of these kind of algorithms to several implementations of the MPI standard and hardware platforms is extensively evaluated in [15], [16] and [17]. Based on analytical communication models, Karonis et al. [18] demonstrated the advantages of a multilevel topology-aware implementation of algorithms with respect to optimal plain algorithms. Sack and Gropp [19] show that a suboptimal algorithm in terms of inter-domain communications may produce lesser congestion that an optimal algorithm, and therefore to achieve a faster execution.

Former approximations adapt algorithms to the underlying communication capabilities. An inverse approach is to improve the performance through the calculation of the best layout of the processes over the processors of the cluster. Kravtsov et al. [20] define and propose an efficient solution to the *topology-aware co-allocation problem*, and Jeannot et al. proposes the *TreeMatch* algorithm in [21] applied to multi-core clusters. The challenge is optimally mapping the graph that defines the communication necessities of an application to the graph of the available resources. The solution can be applied to MPI collective operations, provided that they are built as a set of point-to-point transmissions [22]. Algorithms to automatically build the optimal *distance-aware collective communication topology*, based on the distance information between processes, are proposed in [23]. The results are applied to *Binomial Tree broadcast* and *Ring allgather* collectives.

## III. MPI\_Allreduce Ring Algorithm

In the *MPI\_Allreduce* collective operation every process contributes with a buffer of size *m* bytes and gets in the output buffer the result of applying an specified operation to all the *P* processes buffers.

Ring algorithm implementation of the allreduce collective first copies data from the input buffer to the output buffer. Next, it operates on the output buffer in two phases: *computation* and *distribution*. The algorithm does not preserve order of operations. As a consequence, it can not be used with non commutative operations.

The *computation phase* is done in P - 1 stages. The data buffer is divided up in segments of size m/P. In each stage k, from k = 0, a process p sends its p - k segment to process p + 1, and next receives in a temporary buffer a segment from process p - 1, that operates with local p - k - 1 segment, with wraparounds. The operated segment in each process p has a full operated segment in the p + 1 position of the output buffer.

*Distribution phase* performs an allgather to distribute these segments between processes also using a Ring algorithm. The algorithm operates in P - 1 stages. All processes contribute with an m/P bytes segment at offset p + 1 and receive P segments ordered by rank, for

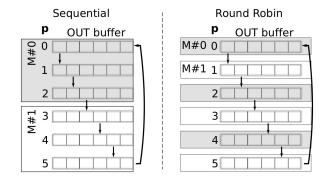

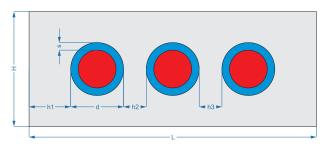

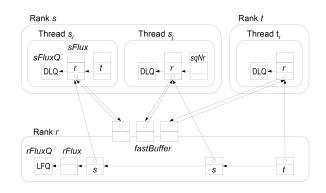

Figure 1: Representation of the communications in the stages of the Allreduce Ring (both computation and distribution phases) algorithm when processes are sequentially and round robin mapped, in a machine with P = 6 processes and M = 2 nodes.

a total of *m* bytes. In each stage, process *p* sends to process p + 1 the m/P bytes received in the previous stage from process p - 1, with wraparound.

Figure 1 represents the transmissions between processes in a machine with P = 6 processes and M = 2 nodes under both sequential (left) and round robin (right) mapping. In the Ring algorithm sequential mapping minimizes the point-to-point transmissions across the network. The first process of each node receives from the former node, and the last process sends to the next node. The rest of transmissions take place in shared memory and they progress in parallel with a total of M inter-node flows. Nevertheless, when the incoming mapping is round-robin  $M \times Q$  inter-node transmissions take place at a time, giving rise to a much higher contention that degrades the communication. In networks as Ethernet, for instance, the contention may lead to a performance breakdown that grows with the number of simultaneous transfers. In section V, we evaluate the performance of Ring algorithm with sequential and round-robin mappings in a cluster based on Infiniband.

The fact is that the layout of the processes over the processors has a great impact in the effective cost. In the allreduce, both phases, computation and distribution, communicate each rank with the nearest next and previous rank numbers, hence, consecutive ranks must run in the same node in order to increase the data transmissions inside a node and minimize the network contention. The next section explores the design of algorithms which take into account the mapping of processes on the physical hierarchy of communications.

#### III.1 Hierarchical Allreduce Algorithm

An algorithm can be designed to minimize the data movement through the slowest communication channels in a multi-core cluster for the allreduce collective. For example, the implementation found in *Open MPI* library is composed of three phases, that progress sequentially.

The first phase performs a *reduce* operation local to each node in the system. One process per node, called local root, obtains the full operated Q segments in the output buffer. The second phase performs an inter-node allreduce between local roots. The number of processes running allreduce decreases with respect to a simple allreduce operation in section III, from *P* to *M*, but the size of messages contributed by each process increases from m/P to  $m \cdot Q/P$ . Thus, the amount of data transmitted through the network is the same as the allreduce Ring algorithm with sequential mapping. Nevertheless, this hierarchical design of the allgather minimizes the network contention regardless of the initial process mapping. Finally, in the third phase, the local root process broadcasts its resulting buffer to the rest of the processes in the same node.

Additional communicators must be created to perform collectives inside each node, and the inter-node allreduce between local roots.

# III.2 Allreduce Mapping Transformation at Run-Time

Under awareness of a regular mapping, such as sequential or roundrobin, the programmer would be in the position of exploiting that knowledge to increase the algorithm performance.

Necessity of minimize network communication advises a physical rearrangement of the processes that guarantees a sequential mapping before starting Ring algorithm. In practice, however, physically moving the processes conveys an excessive latency and cached data invalidation penalties. We propose instead a mere previous logical rearrangement of the ranks, a solution that is applied dynamically and efficiently. Logical renaming of processes ranks can be applied to both computation and distribution phases. The new algorithm is denoted as Ring\*.

Let be a rank set  $R = \{r_0, r_1, \ldots, r_{P-1}\}$  assigned to the *P* processes of a communicator following a Round Robin mapping. For simplicity and without loss of generality, we define  $r_p = p$ . The set *R* can be transformed into another set  $S = \{s_0, s_1, \ldots, s_{P-1}\}$ , which shows a sequential mapping, with  $s_p = f_{SQ}(p)$ . The *transformation function*  $f_{SQ}$  is defined as:

$$f_{SQ}(p) = ((p \times Q) \% P) + \lfloor p / M \rfloor \tag{1}$$

The number of nodes M must be known and the processes must be homogeneously distributed between nodes, i.e., the number of processes per node (Q) must be constant. See section IV for explanations about extensions to irregular mappings.

Similarly, a rank set  $S = \{s_0, s_1, \dots, s_{P-1}\}$  with  $s_p = p$  and a sequential mapping can be transformed into a set  $R = \{r_0, r_1, \dots, r_{P-1}\}$ , which shows a round robin mapping, with  $r_p = f_{RR}(p)$ . The transformation function  $f_{RR}$  (inverse of  $f_{SQ}$ ) is defined as:

$$f_{RR}(p) = ((p \times M) \,\% P) + \lfloor p \,/ \,Q \rfloor \tag{2}$$

In the allreduce computation phase, renaming of processes is applied prior to the execution of the Ring algorithm. A process with rank p behaves as a process with rank  $f_{SQ}(p)$ , applying the definition in (1). Then, in the stage k, a process sends the segment  $f_{SQ}(p) - k$  to process behaving as  $f_{SQ}(p) + 1$ , calculated as  $f_{RR}(f_{SQ}(p) + 1)$ . Next, it receives a segment from process with rank  $f_{RR}(f_{SQ}(p) - 1)$  in a temporary buffer, that operates with local segment  $f_{SQ}(p) - k - 1$ .

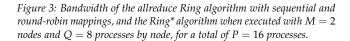

For instance, process p = 2 in Figure 2 behaves as  $f_{SQ}(2) = 1$ . In the first stage k = 0, it sends the segment  $f_{SQ}(2) - k = 1$  to process behaving as the rank  $f_{SQ}(2) + 1$ , which is calculated as  $f_{RR}(f_{SQ}(2) + 1) = f_{RR}(2) = 4$ , and receives from

#### First NESUS Workshop. • October 2014 • Vol. I, No. 1

Figure 2: Allreduce Ring algorithm computation phase, stage k = 0, with round-robin mapping, P = 6 and M = 2. The buffer total size is divided up in P segments. Processes renaming through the transformation functions changes the mapping from round-robin to sequential before starting.

Process

renaming

$f_{RR}(f_{SQ}(2)-1) = f_{RR}(0) = 0$  a segment to be operated with the local segment number  $f_{SQ}(2) - k - 1 = 0$ .

Again, all reduce distribution phase requires renaming of processes from p into  $f_{SQ}(p)$  prior to the execution of the regular Ring all gather algorithm. The operating principle is the same as the computation phase.

#### IV. EXTENSIONS OF THE METHOD

Our approach consists of departing from the a priori knowledge of a layout with regular mapping and keeps the original algorithm after having switched to another regular mapping, much more favourable in terms of performance. Such mapping information could be available through the processes manager module of the particular MPI implementation.

The transformation functions can be applied to algorithms with similar communication patterns to the Ring algorithm. For instance, *Neighbour Exchange* and *Binomial Tree* perform better when processes are sequentially mapped. Other algorithms have opposite requirements, such as *Recursive Doubling* and *Dissemination* algorithms, better suited to initial round robin mapping, because the distance between rank numbers communicating exponentially grows in each stage. The mapping needs to change from sequential to round robin, through the inverse application of the transformation functions.

The above-mentioned algorithms are used in a wide variety of collectives operations defined in the MPI standard, as *Broadcast*, *Scatter*, *Allgather*, etc. proving the method as highly generic.

Nevertheless, we can not always make assumptions about the deployment of the ranks over the cluster, all the more so as this layout may change with the creation of new communicators at run time, that could assign different ranks to the processes. On that case, with non-regular mappings, each rank involved in the collective operation will need to have information about the layout of all the ranks in the communicator. Resource requirements for that information are under study by the authors.

Performance measurements in clusters with other network technologies, such as Ethernet, confirms the expected results, with an increase in the difference of performance between mappings that is proportional to the difference in bandwidth capabilities between the channels.

Message Size (KBvtes)

16 32 64 128 256 512 1M 2M 4M

#### V. Performance Evaluation

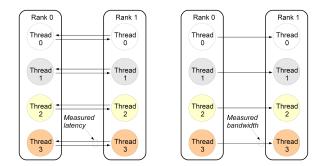

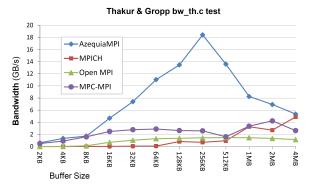

The experimental platform used, named *Fermi*, is composed of eight nodes connected by a QDR Infiniband network. Each node has two 2.27 GHz Quad core Intel Xeon E5520 processors, with 8MB of shared L3 cache size, making a total of eight cores per node. The operating system is Linux 2.6.32. We used IMB (Intel MPI Benchmark), version 3.2, to obtain the latency data. Bandwidth is calculated as the message size divided by the latency, and showed in figures for the sake of clarity. A high number of iterations are executed for each collective algorithm and mean time is taken. IMB runs on Open MPI 1.8, the library that provides the allreduce algorithms through its *Tuned* and *Hierarch* collective components. Nonetheless it should be noted that MVAPICH2 yields similar results, as well as MPICH, which has been tested in Ethernet networks.

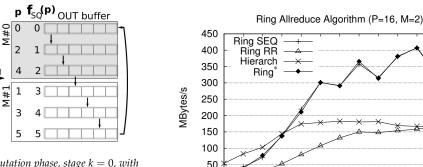

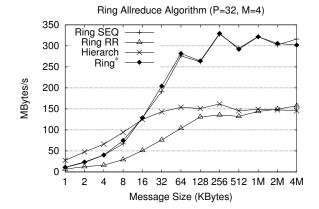

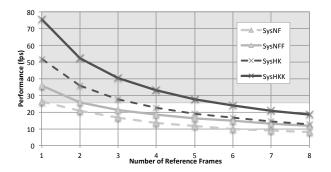

The allreduce Ring algorithm performance is plotted in Figures 3 to 5. Figures represent the bandwidth of sequential (SEQ) and round robin (RR) mappings, as well as the *Ring*<sup>\*</sup> algorithm and the hierarchical implementation of the collective operation, for increasing number of nodes (*M*), with Q = 8. The difference in bandwidth between sequential and *Ring*<sup>\*</sup> algorithm with respect to less favourable round robin mapping is nearly to 2×, for all the range of messages. *Ring*<sup>\*</sup> overload to the Ring algorithm is very low, because it is only attributable to the execution of transformation functions.

Hierarchical implementation of the allreduce algorithm leads to a higher performance than round robin, but it degrades with the size of the message because phases must progress sequentially. Performance depends as well on the algorithms used in each phase. In this paper we use the *binomial tree* algorithm for the *Reduce* and *Broadcast* algorithms in the phases 1 and 3, and allreduce *Ring* algorithm in the inter-node phase 2. This configuration outperforms even the allreduce Ring algorithm for short and medium messages.

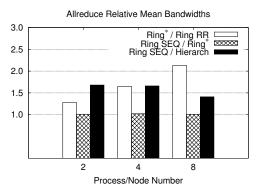

In Figure 6 we plot the relative mean bandwidth (measured along the whole range of messages plotted in figures) between different cases for a constant number of nodes (M = 8), and a growing number of processes per node. Note that the difference between the sequential and the round-robin mapping grows with Q. As expected,

p

3

4

5

M#0 0

M#1

OUT buffer

0

2 4 8

Figure 4: Bandwidth of the allreduce Ring algorithm with sequential and round-robin mappings, and the Ring\* algorithm when executed with M = 4 nodes and Q = 8 processes by node, for a total of P = 32 processes.

the difference between sequential and *Ring*<sup>\*</sup> remains constant, and denotes a minimal overload. Respect to the hierarchical case, the difference is constant for that small number of nodes.

It can be observed in Figure 3 that the change of mapping of the  $Ring^*$  algorithm shows an improvement with respect to the round robin mapping even in a minimal configuration with only M = 2 nodes.

# VI. CONCLUSIONS

The performance of MPI collective algorithms in multi-core clusters highly depends on the deployment of the processes on the processors of the system. These algorithms usually establish a communication pattern between ranks that, if under specific regular mappings, use the communication resources effectively, other mappings significantly worsen their performance. The hierarchical design pursues the optimal use of the system available communication channels, regardless of the process mapping, but they are only efficient in a limited subset of collectives operations.

This paper proposes a more generic approach, whose goal is to adapt the mapping of processes to the communication pattern of the collective algorithm in run-time to reduce network traffic and contention. Such a switch does not require process migration, but a renaming of the processes ranks prior to the execution of the original algorithm.

Performance improvements of *MPI\_Allreduce* collective is evaluated when built upon the *Ring* algorithm, which performs better when processes are mapped sequentially. The figures show that the processes renaming adds a low impact upon the cost of the original algorithm. Results are also compared to the hierarchical implementation of the collective.

Our approach can be applied to other algorithms commonly used in MPI collective operations, as the Recursive Doubling, Neighbour Exchange, Dissemination or Binomial Tree, with different incoming mapping necessities, covering a broad range of communication patterns. In addition, the paper discusses extensions to cover nonregular mapping of processes and other collective operations.

Ring Allreduce Algorithm (P=64, M=8) 300 Ring SEQ Ring RR 250 Hierarch Ring 200 MBytes/s 150 100 50 64 128 256 512 1M 2M 4M 2 4 8 16 32 Message Size (KBytes)

Figure 5: Bandwidth of the allreduce Ring algorithm with sequential and round-robin mappings, and the Ring\* algorithm when executed with M = 8 nodes and Q = 8 processes by node, for a total of P = 64 processes.

# Acknowledgment

The work presented in this paper has been partially supported by EU under the COST programme Action IC1305, 'Network for Sustainable Ultrascale Computing (NESUS)', and by the computing facilities of Extremadura Research Centre for Advanced Technologies (CETA-CIEMAT), funded by the European Regional Development Fund (ERDF). CETA-CIEMAT belongs to CIEMAT and the Government of Spain.

#### References

- MPI Forum. MPI: A Message-Passing Interface Standard, Version 3.0., September 2012.

- [2] MPICH. MPICH High Performance Portable MPI Implementation, 2013.

- [3] Edgar Gabriel, Graham E. Fagg, George Bosilca, Thara Angskun, Jack J. Dongarra, Jeffrey M. Squyres, Vishal Sahay, Prabhanjan Kambadur, Brian Barrett, Andrew Lumsdaine, Ralph H. Castain, David J. Daniel, Richard L. Graham, and Timothy S. Woodall. Open MPI: Goals, concept, and design of a next generation MPI implementation. In *Proceedings*, 11th European PVM/MPI Users' Group Meeting, pages 97–104, Budapest, Hungary, September 2004.

- [4] J. Bruck, Ching-Tien Ho, S. Kipnis, E. Upfal, and D. Weathersby. Efficient algorithms for all-to-all communications in multiport message-passing systems. *Parallel and Distributed Systems, IEEE Transactions on*, 8(11):1143–1156, 1997.

- [5] Jing Chen, Linbo Zhang, Yunquan Zhang, and Wei Yuan. Performance evaluation of allgather algorithms on terascale linux cluster with fast ethernet. In *Proceedings of the Eighth International Conference on High-Performance Computing in Asia-Pacific Region*, HPCASIA '05, pages 437–, Washington, DC, USA, 2005. IEEE Computer Society.

Figure 6: All reduce relative mean bandwidths (calculated for the whole range of messages) of the Ring\* algorithm with respect to the Ring with round robin mapping, of Ring with sequential mapping with respect to Ring\*, and of Ring\* with respect to the hierarchical implementation. All the tests are executed with M = 8 nodes and Q = 8 processes by node, for a total of P = 64 processes.

- [6] Gregory D. Benson, Cho wai Chu, Qing Huang, and Sadik G. Caglar. A comparison of mpich allgather algorithms on switched networks. In *In Proceedings of the 10th EuroPVM/MPI* 2003 Conference, pages 335–343. Springer, 2003.

- [7] Amith R. Mamidala, Abhinav Vishnu, and Dhabaleswar K. Panda. Efficient shared memory and rdma based design for mpi\_allgather over infiniband. In Proceedings of the 13th European PVM/MPI User's Group conference on Recent advances in parallel virtual machine and message passing interface, EuroPVM/MPI'06, pages 66–75, Berlin, Heidelberg, 2006. Springer-Verlag.

- [8] Teng Ma, G. Bosilca, A. Bouteiller, and J.J. Dongarra. Hierknem: An adaptive framework for kernel-assisted and topology-aware collective communications on many-core clusters. In *Parallel Distributed Processing Symposium (IPDPS)*, 2012 IEEE 26th International, pages 970–982, 2012.

- [9] Teng Ma, G. Bosilca, A. Bouteiller, B. Goglin, J.M. Squyres, and J.J. Dongarra. Kernel assisted collective intra-node mpi communication among multi-core and many-core cpus. In *Parallel Processing (ICPP), 2011 International Conference on*, pages 532–541, Sept 2011.

- [10] Thilo Kielmann, Rutger F. H. Hofman, Henri E. Bal, Aske Plaat, and Raoul A. F. Bhoedjang. Magpie: Mpi's collective communication operations for clustered wide area systems. *SIGPLAN Not.*, 34(8):131–140, May 1999.

- [11] Rajeev Thakur, Rolf Rabenseifner, and William Gropp. Optimization of collective communication operations in mpich. *International Journal of High Performance Computing Applications*, 19(1):49–66, 2005.

- [12] Jeffrey M. Squyres and Andrew Lumsdaine. The component architecture of open MPI: Enabling third-party collective algorithms. In Vladimir Getov and Thilo Kielmann, editors, Proceedings, 18th ACM International Conference on Supercomputing,

Workshop on Component Models and Systems for Grid Applications, pages 167–185, St. Malo, France, July 2004. Springer.

- [13] S.S. Vadhiyar, G.E. Fagg, and J. Dongarra. Automatically tuned collective communications. In *Supercomputing*, ACM/IEEE 2000 Conference, pages 3–3, Nov 2000.

- [14] Meng-Shiou Wu, R.A. Kendall, and K. Wright. Optimizing collective communications on smp clusters. In *Parallel Processing*, 2005. ICPP 2005. International Conference on, pages 399–407, 2005.

- [15] Hao Zhu, David Goodell, William Gropp, and Rajeev Thakur. Hierarchical collectives in mpich2. In *Proceedings of the 16th European PVM/MPI Users' Group Meeting on Recent Advances in Parallel Virtual Machine and Message Passing Interface*, pages 325–326, Berlin, Heidelberg, 2009. Springer-Verlag.

- [16] A.R. Mamidala, R. Kumar, D. De, and D.K. Panda. Mpi collectives on modern multicore clusters: Performance optimizations and communication characteristics. In *Cluster Computing and the Grid*, 2008. CCGRID '08. 8th IEEE International Symposium on, pages 130–137, 2008.

- [17] Richard L. Graham and Galen Shipman. Mpi support for multicore architectures: Optimized shared memory collectives. In *Proceedings of the 15th European PVM/MPI Users' Group Meeting on Recent Advances in Parallel Virtual Machine and Message Passing Interface*, pages 130–140, Berlin, Heidelberg, 2008. Springer-Verlag.

- [18] Nicholas T. Karonis, Bronis R. de Supinski, Ian T. Foster, William Gropp, and Ewing L. Lusk. A multilevel approach to topologyaware collective operations in computational grids. *CoRR*, cs.DC/0206038, 2002.

- [19] Paul Sack and William Gropp. Faster topology-aware collective algorithms through non-minimal communication. *SIGPLAN Not.*, 47(8):45–54, February 2012.

- [20] Valentin Kravtsov, Martin Swain, Uri Dubin, Werner Dubitzky, and Assaf Schuster. A fast and efficient algorithm for topologyaware coallocation. In *Proceedings of the 8th international conference on Computational Science, Part I*, ICCS '08, pages 274–283, Berlin, Heidelberg, 2008. Springer-Verlag.

- [21] E. Jeannot, G. Mercier, and F. Tessier. Process placement in multicore clusters: algorithmic issues and practical techniques. *Parallel and Distributed Systems, IEEE Transactions on*, 25(4):993– 1002, April 2014.

- [22] Jin Zhang, Jidong Zhai, Wenguang Chen, and Weimin Zheng. Process mapping for mpi collective communications. In Proceedings of the 15th International Euro-Par Conference on Parallel Processing, Euro-Par '09, pages 81–92, Berlin, Heidelberg, 2009. Springer-Verlag.

- [23] Teng Ma, T. Herault, G. Bosilca, and J.J. Dongarra. Process distance-aware adaptive mpi collective communications. In *Cluster Computing (CLUSTER), 2011 IEEE International Conference* on, pages 196–204, 2011.

7

# A Workflow-oriented Language for Scalable Data Analytics

Fabrizio Marozzo, Domenico Talia, Paolo Trunfio

DIMES - University of Calabria, Italy

fmarozzo@dimes.unical.it, talia@dimes.unical.it, trunfio@dimes.unical.it

#### Abstract

Data in digital repositories are everyday more and more massive and distributed. Therefore analyzing them requires efficient data analysis techniques and scalable storage and computing platforms. Cloud computing infrastructures offer an effective support for addressing both the computational and data storage needs of big data mining and parallel knowledge discovery applications. In fact, complex data mining tasks involve data- and compute-intensive algorithms that require large and efficient storage facilities together with high performance processors to get results in acceptable times. In this paper we describe a Data Mining Cloud Framework (DMCF) designed for developing and executing distributed data analytics applications as workflows of services. We describe also a workflow-oriented language, called JS4Cloud, to support the design and execution of script-based data analysis workflows on DMCF. We finally present a data analysis application developed with JS4Cloud, and the scalability achieved executing it on DMCF.

Keywords Cloud computing, Data analytics, Workflows, JS4Cloud

#### I. INTRODUCTION

Cloud computing provides elastic services, high performance and scalable data storage to a large and everyday increasing number of users [1]. Clouds enlarged the offer of distributed computing systems by providing advanced Internet services that complement and complete functionalities of distributed computing provided by the Web, Grid computing and peer-to-peer networks. In fact, Cloud computing systems provide large-scale infrastructures for complex high-performance applications. Most of those applications use big data repositories and needs to access and analyze them to extract useful information.

Big data is a new and over-used term that refers to massive, heterogeneous, and often unstructured digital content that is difficult to process using traditional data management tools and techniques. The term includes the complexity and variety of data and data types, real-time data collection and processing needs, and the value that can be obtained by smart analytics. Advanced data mining techniques and associated tools can help extract information from large, complex datasets that are useful in making informed decisions in many business and scientific applications including advertising, market sales, social studies, bioinformatics, and high-energy physics. Combining big data analytics and knowledge discovery techniques with scalable computing systems will produce new insights in a shorter time [5].

Although a few cloud-based analytics platforms are available today, current research work foresees that they will become common within a few years. Some current solutions are open source systems such as Apache Hadoop and SciDB, while others are proprietary solutions provided by companies such as Google, IBM, EMC, BigML, Splunk Storm, Kognitio, and InsightsOne. As more such platforms emerge, researchers will port increasingly powerful data mining programming tools and strategies to the cloud to exploit complex and flexible software models such as the distributed workflow paradigm.

The growing use of service-oriented computing could accelerate

this trend. Developers and researchers can adopt the software as a service (SaaS), platform as a service (PaaS), and infrastructure as a service (IaaS) models to implement big data analytics solutions in the cloud. In such a way, data mining tasks and knowledge discovery applications can be offered as high-level services on Clouds. This approach creates a new way to delivery data analysis software that is called data analytics as a service (DAaaS).

Here we describe a Data Mining Cloud Framework (DMCF) that we developed according to this approach. In DMCF, data analysis workflows can be designed through visual programming, which is a very effective design approach for high-level users, e.g. domainexpert analysts having a limited understanding of programming. Recently, we extended the DMCF system to support also script-based data analysis workflows, as an additional and more flexible programming interface for skilled users. To this end, in [4] we introduced a workflow-oriented language, called JS4Cloud, to support the design and execution of script-based data analysis workflows on DMCF.

# II. DATA MINING CLOUD FRAMEWORK

The DMCF has been designed to be implemented on different Cloud systems. However, a first implementation of the framework has been carried out on the Windows Azure cloud platform and has been evaluated through a set of data analysis applications executed on a Microsoft Cloud data center. The remainder of the section describes system architecture, application execution, user interface, and visual workflow programming.

#### **II.1** System architecture

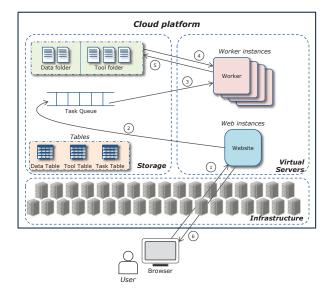

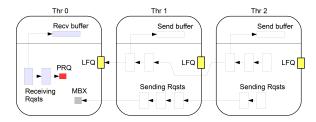

The architecture includes different kinds of components that can be grouped into storage and compute components (see Figure 1). The storage components include:

• A Data Folder that contains data sources and the results of

knowledge discovery processes. Similarly, a *Tool folder* contains libraries and executable files for data selection, pre-processing, transformation, data mining, and results evaluation.

- The *Data Table, Tool Table* and *Task Table* that contain metadata information associated with data, tools, and tasks.

- The *Task Queue* that manages the tasks to be executed.

Figure 1: System architecture and application execution steps.

The virtual machines components are:

- A pool of *Worker instances*, which is in charge of executing the data mining tasks submitted by users.

- A pool of *Web instances* host the Website, by allowing users to submit, monitor the execution, and access the results of their data mining tasks.

The Website is the user interface to three functionalities: i) *App submission*, which allows users to submit single-task, parameter sweeping, or workflow-based applications; ii) *App monitoring*, which is used to monitor the status and access results of the submitted applications; iii) *Data/Tool management*, which allows users to manage input/output data and tools.

#### **II.2** Applications execution

Figure 1 shows the main steps carried out for designing and executing a knowledge discovery application:

- 1. A user accesses the Website and designs the application (either single-task, parameter sweeping, or workflow-based) through a Web-based interface.

- After application submission, the system creates a set of tasks and inserts them into the Task Queue on the basis of the application.

- 3. Each idle Worker picks a task from the Task Queue, and concurrently executes it.

- 4. Each Worker gets the input dataset from the location specified by the application. To this end, a file transfer is performed from the Data Folder where the dataset is located, to the local storage of the Worker.

- 5. After task completion, each Worker puts the result on the Data Folder.

- The Website notifies the user as soon as her/his task(s) have completed, and allows her/him to access the results.

The set of tasks created on the second step depends on the type of application submitted by a user. In the case of a single-task application, just one data mining task is inserted into the Task Queue. If the user submits a parameter sweeping application, the set of tasks corresponding to the combinations of the input parameters values are executed in parallel. If a complex workflow-based application must be executed, the set of tasks created depends on how many data mining tools are invoked within the workflow. Initially, only the workflow tasks without dependencies are inserted into the Task Queue.

# II.3 User interface

The App submission section of the Website is composed of two main parts: one pane for composing and running both single-task and parameter-sweeping applications and another pane for programming and executing workflow-based knowledge discovery applications. As an example, Figure 2 shows a screenshot of the App submission section, taken during the execution of a parameter-sweeping application.

| Data Mining Cloud Framework   |                                                                             |                    |                        |                |  |  |

|-------------------------------|-----------------------------------------------------------------------------|--------------------|------------------------|----------------|--|--|

| App submiss                   | ion                                                                         | App monitoring     | Data/Tool management   | About          |  |  |

| Paramete                      | Parameter sweeping                                                          |                    |                        |                |  |  |

| Select algorith<br>Algorithm: | Select algorithm and parameters:<br>Algorithm: weka.clusterers.SimpleKMeans |                    |                        |                |  |  |

| Dataset:                      | USCensi                                                                     | us_20MB-n.arff     | ✓ or <u>upload new</u> |                |  |  |

| 🗵 Number of                   | clusters                                                                    | from: 2            | to: 9 by: 1            | « remove sweep |  |  |

| Seed Seed                     |                                                                             | list of values: 12 | 211,1311               | « remove sweep |  |  |

| Submit                        |                                                                             |                    |                        |                |  |  |

Figure 2: Screenshot of the App submission section.

Users can monitor the status of each single task through the App monitoring section, as shown in Figure 3. For each task, the current status (submitted, running, done or failed) and status update time are shown. Moreover, for each task that has completed its execution, two links are enabled: the first one (Stat) gives access to a file containing some statistics about the amount of resources consumed by the task; the second one (Result) visualizes the task result.

#### First NESUS Workshop. October 2014

| Data Mining Cloud Framework |       |               |                     |             |               |         |

|-----------------------------|-------|---------------|---------------------|-------------|---------------|---------|

| App submission              | Ар    | o monitoring  | Data/Tool manag     | ement       | About         |         |

| Task status                 |       |               |                     |             |               |         |

| Task ID                     |       | CurrentStatus | StatusUpdateTime    | Statistics  | Result        | Archive |

| 163445411882436235          | 8-001 | done          | 7/4/2011 7:34:08 PM | <u>Stat</u> | <u>Result</u> | ×       |

| 163445411882436235          | 8-002 | done          | 7/4/2011 7:33:10 PM | Stat        | Result        | ×       |

| 163445411882436235          | 8-003 | done          | 7/4/2011 7:34:00 PM | <u>Stat</u> | <u>Result</u> | ×       |

| 163445411882436235          | 8-004 | done          | 7/4/2011 7:34:19 PM | Stat        | Result        | ×       |

| 163445411882436235          | 8-005 | running       | 7/4/2011 7:33:11 PM | Stat        | Result        | ×       |

Figure 3: Screenshot of the App monitoring section.

## II.4 Visual workflow programming

The DMCF includes a visual programming interface and its services to support the composition and execution of workflow-based knowledge discovery applications. Workflows provide a paradigm that may encompass all the steps of discovery based on the execution of complex algorithms and the access and analysis of scientific data. In data-driven discovery processes, knowledge discovery workflows can produce results that can confirm real experiments or provide insights that cannot be achieved in laboratories.

Visual workflows in DMCF are directed acyclic graphs whose nodes represent resources and whose edges represent the dependencies among the resources. Workflows include two types of nodes:

- *Data* node, which represents an input or output data element. Two subtypes exist: Dataset, which represents a data collection, and Model, which represents a model generated by a data analysis tool (e.g., a decision tree).

- *Tool* node, which represents a tool performing any kind of operation that can be applied to a data node (filtering, splitting, data mining, etc.).

The nodes can be connected with each other through direct edges, establishing specific dependency relationships among them. When an edge is being created between two nodes, a label is automatically attached to it representing the kind of relationship between the two nodes. Data and Tool nodes can be added to the workflow singularly or in array form. A data array is an ordered collection of input/output data elements, while a tool array represents multiple instances of the same tool.

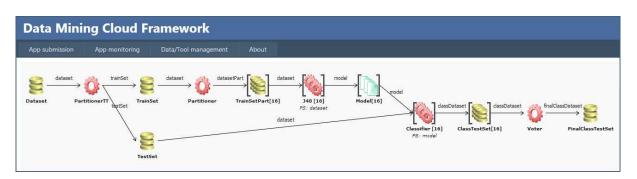

Figure 4 shows a data mining workflow composed of several sequential and parallel steps as an example for presenting the main features of the visual programming interface of the DMCF [3]. The example workflow analyzes a dataset by using several instances of a classification algorithm that run in parallel on several cloud servers.

#### III. SCRIPT-BASED WORKFLOW PROGRAMMING

JS4Cloud (JavaScript for Cloud) is a JavaScript-based language for programming data analysis workflows [4]. The Web interface of DMCF allows to design and execute workflows programmed by the JS4Cloud language, by providing an environment similar to that used to develop visual workflows in the same framework. The main benefits of JS4Cloud are: i) it is based on a well known scripting language, so that users do not have to learn a new programming language from scratch; ii) it implements a data-driven task parallelism that automatically spawns ready-to-run tasks to the available Cloud resources; iii) it exploits implicit parallelism so application workflows can be programmed in a totally sequential way.

Two key programming abstractions in JS4Cloud are *Data* and *Tool* elements:

- *Data* elements denote input files or storage elements, or output files or stored elements.

- Tool elements denote algorithms or software tools.

For each Data and Tool element included in a JS4Cloud workflow, an associated descriptor, expressed in JSON format, will be included in the environment of the user who is developing the workflow.

A Tool descriptor includes a reference to its executable, the required libraries, and the list of input and output parameters. Each parameter is characterized by name, description, type, and can be mandatory or optional. The JSON descriptor of a new tool is created automatically through a guided procedure provided by DMCF, which allows users to specify all the needed information for invoking the tool (executable, input and output parameters, etc.).

Similarly, a Data descriptor contains information to access an input or output file, including its identifier, location, and format. Differently from Tool descriptors, Data descriptors can also be created dynamically as a result of a task operation during the execution of a JS4Cloud script. For example, if a workflow *W* reads a dataset  $D_i$  and creates (writes) a new dataset  $D_j$ , only  $D_i$ 's descriptor will be present in the environment before *W*'s execution, whereas  $D_j$ 's descriptor will be created at runtime.

Another key element in JS4Cloud is the *task* concept, which represents the unit of parallelism in our model. A task is a Tool, invoked from the script code, which is intended to run in parallel with other tasks on a set of Cloud resources.

According to this approach, JS4Cloud implements *data-driven task parallelism*. This means that, as soon as a task does not depend on any other task in the same workflow, the runtime asynchronously spawns it to the first available virtual machine. A task  $T_j$  does not depend on a task  $T_i$  belonging to the same workflow (with  $i \neq j$ ), if  $T_j$  during its execution does not read any data element created by  $T_i$ .

# III.1 JS4Cloud functions

JS4Cloud extends JavaScript with three additional functionalities, implemented by the set of functions listed in Table 1:

- Data Access, for accessing a data element stored in the Cloud;

- *Data Definition*: to define a new data element that will be created at runtime as a result of a tool execution;

- *Tool Execution*: to invoke the execution of a tool available in the Cloud.

Figure 4: A visual workflow for parallel classification.

Table 1: JS4Cloud functions.

| Functionality      | Function                                                                                    | Description                                                                                  |

|--------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Data               | Data.get( <dataname>);</dataname>                                                           | Returns a reference to the data element with the provided name.                              |

| Access             | Data.get(new RegExp( <regular expression="">));</regular>                                   | Returns an array of references to the data elements whose name match the regular expression. |

|                    | Data.define( <dataname>);</dataname>                                                        | Defines a new data element that will be created at run-<br>time.                             |

| Data<br>Definition | Data.define( <arrayname>,<dim>);</dim></arrayname>                                          | Define an array of data elements.                                                            |

|                    | Data.define( <arrayname>,[<dim<sub>1&gt;,,<dim<sub>n&gt;]);</dim<sub></dim<sub></arrayname> | Define a multi-dimensional array of data elements.                                           |

| Tool<br>Execution  | <toolname>(<par1>:<val1>,,<par1>:<val1>);</val1></par1></val1></par1></toolname>            | Invokes an existing tool with associated parameter values.                                   |

Data Access is implemented by the Data.get function, which is available in two versions: the first one receives the name of a data element, and returns a reference to it; the second one returns an array of references to the data elements whose name match the provided regular expression. For example, the following statement:

var ref = Data.get("Census");

assigns to variable ref a reference to the dataset named Census, while the following statement:

var ref = Data.get(new RegExp("^CensusPart"));

assigns to ref an array of references (ref[0]...ref[n-1]) to all the datasets whose name begins with CensusPart.

Data Definition is done through the Data.define function, available in three versions: the first one defines a single data element; the second one defines a one-dimensional array of data elements; the third one defines a multi-dimensional array of data elements. For instance, the following piece of code:

var ref = Data.define("CensusModel");

defines a new data element named CensusModel and assigns its reference to variable ref, while the following statement:

```

var ref = Data.define("CensusModel", 16);

```

defines an array of data elements of size 16 (ref[0]... ref[15]). In both cases, the data elements will be created at runtime as result of a tool execution.

Differently from Data Access and Data Definition, there is not a named function for Tool Execution. In fact, the invocation of a tool T is made by calling a function with the same name of T. For example, the following statement:

DTree({dataset:DRef, confidence:0.05, model:MRef});

invokes a tool named DTree, where DRef is a reference to the dataset to be analyzed, previously introduced using the Data.get function, MRef is a reference to the model to be generated, previously introduced using Data.define.

# **III.2** Basic patterns

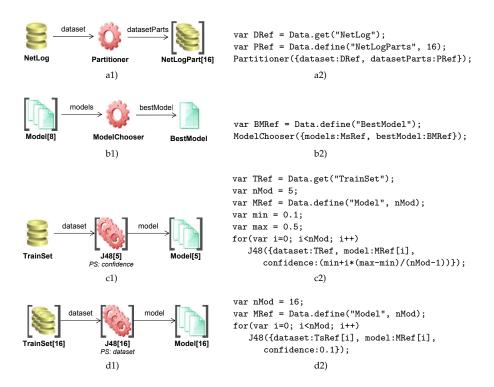

Several workflow patterns can be implemented with JS4Cloud [4]. Figure 5 shows four examples of patterns that can be defined in JS4Cloud workflows, namely data partitioning, data aggregation, parameter sweeping and input sweeping. For each pattern, the figure shows an example as a visual DMCF workflow, and how the same example can be coded using JS4Cloud.

The *data partitioning* pattern produces two or more output data from an input data element, as in Figure 5-a1, where a Partitioner tool divides a dataset into a number of splits. With JS4Cloud, this can be written as shown in Figure 5-a2.

First NESUS Workshop. October 2014

Figure 5: Visual (left) and JS4Cloud (right) workflow patterns: a) data partitioning; b) data aggregation; c) parameter sweeping; d) input sweeping.

The *data aggregation* pattern generates one output data from multiple input data, as in Figure 5-b1, where a ModelChooser tool takes as input eight data mining models and chooses the best one based on some evaluation criteria. The same task can be coded using JS4Cloud as shown in Figure 5-b2.

*Parameter sweeping* is a data analysis pattern in which a dataset is analyzed by multiple instances of the same tool with different parameters, as in the example shown in Figure 5-c1. In this example, a training set is processed in parallel by 5 instances of the J48 data classification tool to produce the same number of data mining models. The J48 instances differ each other by the value of a single parameter, the *confidence* factor, which has been configured (through the visual interface) to range from 0.1 to 0.5 with a step of 0.1. The equivalent JS4Cloud script is shown in Figure 5-c2.

Finally, *input sweeping* is a pattern in which a set of input data is analyzed independently to produce the same number of output data. It is similar to the parameter sweeping pattern, with the difference that in this case the sweeping is done on the input data rather than on a tool parameter. An example of input sweeping pattern is represented in Figure 5-d1. In this example, 16 training sets are processed in parallel by 16 instances of J48, to produce the same number of data mining models. The corresponding JS4Cloud script is shown in Figure 5-d2.

#### III.3 Example of JS4Cloud workflow

We describe a JS4Cloud workflow that analyzes a dataset using n instances of the J48 classification algorithm that work on n partitions

of the training set and generate n knowledge models. By using the n generated models and the test set, n classifiers produce in parallel n classified datasets (n classifications). In the final step of the workflow, a voter generates the final classification (in the file FinalClassTestSet) by assigning a class to each data item. This is done by choosing the class predicted by the majority of the models [6].

The input dataset, containing about 46 million tuples and with a size of 5 GB, was generated from the *KDD Cup* 1999's dataset, which contains a wide variety of simulated intrusion records in a military network environment.

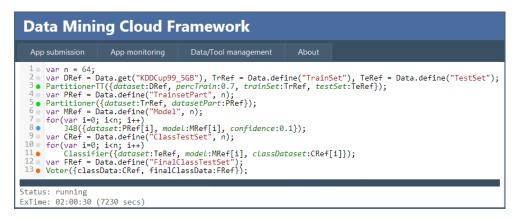

Figure 6 shows the JS4Cloud code of the workflow. At the beginning, the input dataset is split into training set and test set by a partitioning tool (*line 3*). Then, the training set is partitioned into 64 parts using another partitioning tool (*line 5*). As third step, the training sets are analyzed in parallel by 64 instances of the J48 classification algorithm, to produce the same number of classification models (*lines 7-8*). The fourth step classifies the test set using the 64 models generated on the previous step (*lines 10-11*). The classification is performed by 64 classifiers that run in parallel to produce 64 classified test sets. As the last operation, the 64 classified test sets are passed to a voter that produces the final classified test set.

Beside each code line number, a colored circle indicates the status of execution. The green circles at lines 3 and 5 indicate that the two partitioners have completed their execution; the blue circle at line 8 indicates that J48 tasks are still running; the orange circles indicates that the corresponding tasks are waiting to be executed.

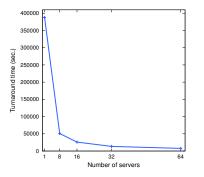

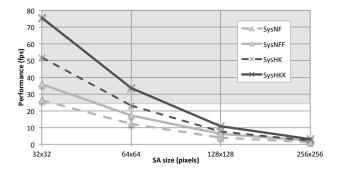

Figure 7 shows the turnaround times of the workflow, obtained

First NESUS Workshop. October 2014

Figure 6: JS4Cloud workflow running in the DMCF's user interface.

varying the number of virtual servers used to run it on the Cloud from 1 (sequential execution) to 64 (maximum parallelism). As shown in the figure, the turnaround time decreases from more than 107 hours (4.5 days) by using a single server, to about 2 hours on 64 servers. This is an evident and significant reduction of time, with a speedup ranging from 7.64 using 8 servers to 50.78 using 64 servers. This is a very positive result, taking into account that some sequential parts of the implemented application (namely, partitioning and voting) do not run in parallel.

Figure 7: Turnaround time vs number of available servers.

#### IV. CONCLUDING REMARKS

Cloud computing [2] provides scalable resources for Big data mining and parallel knowledge discovery applications. In fact, Clouds offer large and efficient storage facilities with high performance processors to get results in reduced times. In this paper we presented a Data Mining Cloud Framework (DMCF) designed for developing and running distributed data analytics applications as collections of services. In this framework, data sets, data mining algorithms and knowledge models are implemented as services that can be combined through a visual interface to produce distributed workflows executed on Clouds.

Recently, we extended the DMCF system to support also script-

based data analysis workflows, as an additional and more flexible programming interface for skilled users. To this end, we introduced a workflow-oriented language, called JS4Cloud, to support the design and execution of script-based data analysis workflows on DMCF. Experimental performance results, obtained designing and executing JS4Cloud workflows in DMCF, have proven the effectiveness of the proposed language for programming data analysis workflows, as well as the scalability that can be achieved by executing such workflows on a public Cloud infrastructure.

#### Acknowledgment

The work presented in this paper has been partially supported by EU under the COST programme Action IC1305, 'Network for Sustainable Ultrascale Computing (NESUS)'.

#### References

- Michael Armbrust, Armando Fox, Rean Griffith, Anthony D. Joseph, Randy Katz, Andy Konwinski, Gunho Lee, David Patterson, Ariel Rabkin, Ion Stoica, and Matei Zaharia. A view of cloud computing. *Commun. ACM*, 53(4):50–58, April 2010.

- [2] Cloud Computing Expert Group. The future of cloud computing. Report from European Commission, January 2010.

- [3] F. Marozzo, D. Talia, and P. Trunfio. A cloud framework for big data analytics workflows on azure. In *Proc. of the 2012 High Performance Computing Workshop, HPC 2012.* 2012.

- [4] Fabrizio Marozzo, Domenico Talia, and Paolo Trunfio. Scalable script-based data analysis workflows on clouds. In *Proc. of the 8th Workshop on Workflows in Support of Large-Scale Science (WORKS* 2013), pages 124–133, Denver, CO, USA, November 2013. ACM Press.

- [5] Domenico Talia. Clouds for scalable big data analytics. *IEEE Computer*, 46(5):98–101, 2013.

- [6] Z.-H. Zhou and M. Li. Semi-supervised learning by disagreement. *Knowl. Inf. Syst.*, 24(3):415–439, 2010.

# Scheduling Real-Time Jobs in Distributed Systems - Simulation and Performance Analysis

Georgios L. Stavrinides and Helen D. Karatza

Aristotle University of Thessaloniki, Greece gstavrin@csd.auth.gr, karatza@csd.auth.gr

#### Abstract

One of the major challenges in ultrascale systems is the effective scheduling of complex jobs within strict timing constraints. The distributed and heterogeneous system resources constitute another critical issue that must be addressed by the employed scheduling strategy. In this paper, we investigate by simulation the performance of various policies for the scheduling of real-time directed acyclic graphs in a heterogeneous distributed environment. We apply bin packing techniques during the processor selection phase of the scheduling process, in order to utilize schedule gaps and thus enhance existing list scheduling methods. The simulation results show that the proposed policies outperform all of the other examined algorithms.

Keywords Scheduling, Distributed systems, Real-time jobs, Simulation, Performance evaluation

# I. INTRODUCTION

The rapid developments in computing and communication technologies have led to the emergence of *ultrascale computing*, which provides a large-scale, heterogeneous distributed platform for the processing of complex jobs [1, 2, 3, 4]. The sustainability of a computing environment of such scale and complexity is one of the most crucial aspects of ultrascale computing.

#### I.1 Motivation

One of the major challenges in ultrascale systems is the *effective scheduling* and processing of a large number of *interdependent* tasks within strict *timing constraints*. Such tasks often have precedence constraints among them and thus form a *real-time directed acyclic graph* (*DAG*), with an end-to-end deadline. In case a real-time job cannot meet its deadline, then depending on its criticality, its result will be useless or even worse, this may have catastrophic consequences on the environment under control [5]. The *distributed* and *heterogeneous* resources of the target system constitute another critical issue that must be addressed during the scheduling of real-time complex jobs [6].

# I.2 Contribution

We investigate by simulation the performance of various policies for the scheduling of real-time DAGs in a heterogeneous distributed environment. Our goal is to apply *effective techniques* during the scheduling process, in order to guarantee that every real-time job will meet its deadline.

#### I.3 Related Work

A large number of job scheduling techniques have been developed and studied in the literature [7, 8, 9, 10, 11, 12, 13]. The most commonly used real-time scheduling algorithm is the *Earliest Deadline First (EDF)* [14]. According to this policy, the job with the earliest deadline has the highest priority for execution. An efficient and practical method for scheduling directed acyclic graphs, is the *list scheduling approach*, according to which the tasks are arranged in a prioritized list. Subsequently, each task is allocated to the processor that minimizes a cost function, such as the task estimated start time [15]. A simple list scheduling algorithm is the *Highest Level First (HLF)* [16], which prioritizes each component task according to the longest path from the particular task to an exit task in the DAG.

Based on the observation that idle time slots may form in the schedule of a processor due to the data dependencies of the tasks in a DAG, Kruatrachue and Lewis in [17] propose the *Insertion Scheduling Heuristic (ISH)*. According to this method which is based on HLF, during the processor selection phase, a task may be inserted into an idle time slot in a processor's schedule, as long as it does not delay the execution of the succeeding task in the schedule and provided that it cannot start earlier on any other processor. Topcuoglu et al. in [18] present the *Heterogeneous Earliest Finish Time (HEFT)* list scheduling strategy, which is essentially an alternative version of ISH, adapted for heterogeneous systems.

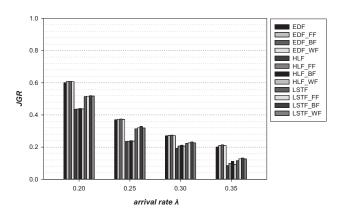

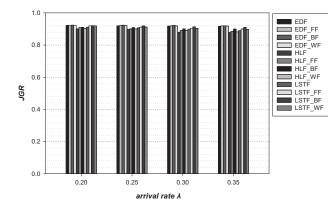

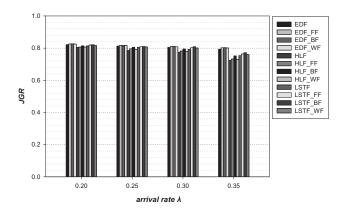

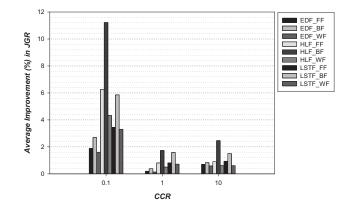

An improved version of HEFT is presented in [15] by Arabnejad and Barbosa. It introduces a look ahead feature based on an optimistic cost table. Jiang et al. in [19] present a novel clustering algorithm, the *Path Clustering Heuristic with Distributed Gap Search* (*PCH-DGS*), for the scheduling of multiple DAGs in a heterogeneous cloud. Their proposed method tries to insert each group of tasks into the first available idle time slot in a processor's schedule (a DAG's tasks are partitioned into groups in an attempt to minimize the communication cost between them). In case the time gap cannot accommodate all of the tasks of the group, the rest of the group's tasks are inserted into the next available schedule gap of the same or other processor. All of the above algorithms are static and do not take into account any timing constraints. Moreover, they essentially utilize schedule gaps according to the First Fit bin packing technique [20]. Cheng et al. propose in [21] a scheduling heuristic, *Least Space-Time First* (*LSTF*), that takes into account both the precedence and the timing constraints among the tasks. However, their algorithm does not utilize any schedule idle time slots. In this paper, we apply various bin packing techniques (First Fit, Best Fit and Worst Fit) during the processor selection phase of the scheduling process, in order to utilize schedule gaps and thus enhance existing list scheduling methods. Moreover, our policies are suitable for the dynamic scheduling of multiple real-time DAGs.

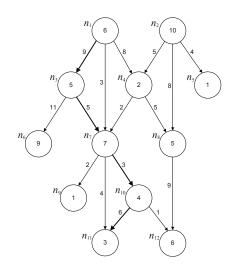

#### II. System and Workload Models

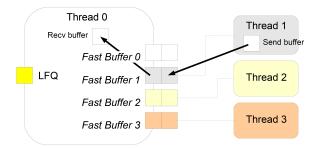

The real-time complex jobs arrive in a Poisson stream with rate  $\lambda$  at a heterogeneous cluster that consists of a set of q fully connected processors. Each processor  $p_i$  serves its own local queue of tasks (it has its own local memory) and has an execution rate  $\mu_i$ . The transfer rate between two processors  $p_i$  and  $p_j$  is denoted by  $v_{ij}$ . The processor execution rates and the communication links data transfer rates may vary. The heterogeneous cluster is dedicated to real-time jobs and it may be part of a computational grid or cloud. The jobs arrive at a central scheduler [22], where their unscheduled tasks wait in a global waiting queue until they get ready to be scheduled. A task becomes ready to be scheduled when it has no predecessors or when all of its parent tasks have finished execution.